# IZE4406

# Intelligent 104-Bit EEPROM Counter for > 20000 Units with Security Logic

The chip contains an EEPROM/PROM of 88 bits, a mask ROM of 16 bits and a sequencing control with security logic.

Memory (104 bits) is divided into the following functional areas

In the condition as supplied, the transport code and the error counter are activated. The chip can only be read (except for the transport-code area) and only the error counter can be written.

Following correct entry of the transport code, the entire memory can be read and areas II and III can be written and EEPROM part of area III can be erased.

After the control flag has been written, everything is readable and only area III can be programmed, but with the following changes:

- The transport code and the error counter are no longer activated.

- The area of the former transport code and the error counter can be erased byte by byte with carry.

- The entire area III can be written bit by bit

NB: When the control flag is written, the counter stage below it (the error counter) can be erased at the same time.

## FEATURES

- 104 x 1 bit organization

- Three memory areas with special characteristics (eg ROM, PROM, EEPROM)

- Maximum of 20480 count units

- Special security features

- Minimum of 10<sup>4</sup> write/erase cycles

- Data retention for minimum of ten years

• Contact configuration and serial interface in accordance to ISO standard 7816-3 (synchronous transmission)

### PIN DEFINITIONS AND FUNCTIONS

| Card Contact | Pad № | Symbol | Function                                 |

|--------------|-------|--------|------------------------------------------|

| C7           | 01    | I/O    | Bidirectional data line (open drain)     |

|              |       |        | Code entry on "Input" only for transport |

|              | 02    | Р      | Test input                               |

| C3           | 03    | CLC    | Clock input                              |

| C2           | 04    | RST    | Control input (reset)                    |

| C1           | 05    | Vcc    | Supply voltage                           |

| C6           |       | N.C.   | Not connected                            |

| C5           | 06    | GND    | Ground                                   |

IZ4406 comes as an M1 wire-bonded module for embedding in plastic cards and as a die for customer packaging

| 1  | ROM         | This area contains unalterable chip data (eg application, design status).<br>Part of the data is entered by way of a ROM mask and the remainder<br>when testing. Both parts are unalterable.                                                                                                                                                                                                                                                                                              |

|----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| II | PROM        | In this area the user can enter card data for a particular application. A control flag can be set to safeguard this area against alteration.                                                                                                                                                                                                                                                                                                                                              |

|    | PROM/EEPROM | This area contains the count data and stores the current count in<br>nonvolatile memory. The individual counter stages with carry can be<br>erased (ie EEPROM), only the uppermost counter stage not being<br>erasable (ie PROM).<br>Before the control flag is set, part of the EEPROM area contains a secret<br>transport code. Another part serves as an error counter.<br>Function of the PROM area:<br>1 bit: Control flag<br>3 bits: Test bits for manufacturer<br>4 bits: for user |

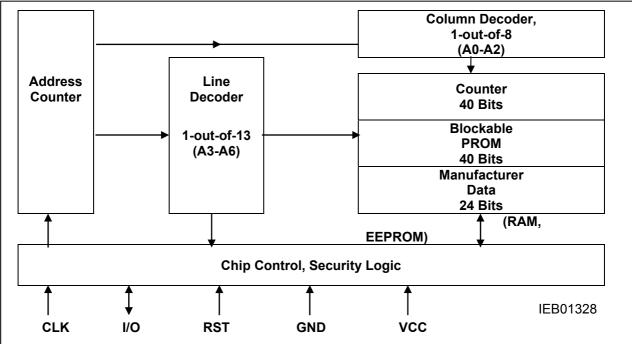

### BLOCK DIAGRAM

### ABSOLUTE MAXIMUM RATINGS

| Parameter           | Symbol           | Limit Values |      | Unit | Comments |

|---------------------|------------------|--------------|------|------|----------|

|                     | -                | Min.         | Max. | ]    |          |

| Supply voltage      | V <sub>cc</sub>  | -0.3         | 6    | V    | -        |

| Input voltage       | Vi               | -0.3         | 6    | V    | -        |

| Storage temperature | T <sub>stg</sub> | -60          | 125  | °C   |          |

| Power dissipation   | P <sub>tot</sub> |              | 27,5 | MW   | -        |

#### **OPERATING RANGE**

| Parameter           | Symbol          | Limit Values |      | Limit Values |   | Unit | Comments |

|---------------------|-----------------|--------------|------|--------------|---|------|----------|

|                     |                 | Min.         | Max. |              |   |      |          |

| Supply voltage      | V <sub>cc</sub> | 4.75         | 5.5  | V            | - |      |          |

| Ambient temperature | T <sub>A</sub>  | -35          | 80   | О°           | - |      |          |

# IZE4406

| Parameter                                 | Symbol          | Limit Values |      |                 | Unit | Test<br>Condition |

|-------------------------------------------|-----------------|--------------|------|-----------------|------|-------------------|

|                                           |                 | Min.         | Тур. | Max.            |      |                   |

| SUPPLY                                    | · · · ·         |              |      |                 |      | •                 |

| Supply voltage                            | V <sub>CC</sub> | 4.75         | 5    | 5.5             | V    | -                 |

| Supply current                            | I <sub>CC</sub> |              | 1.5  | 5               | mA   | -                 |

| DATA INPUT                                |                 |              |      |                 |      |                   |

| H-Input voltage (I/O,CLC,P,RST)           | V <sub>H</sub>  | 3.5          | -    | V <sub>CC</sub> | V    | -                 |

| L-Input voltage (I/O,CLC,RST)             | VL              | 0            | -    | 0.8             | V    | -                 |

| L-Input current (CLC)                     | I <sub>H</sub>  | -            | -    | 100             | μA   | -                 |

| (V <sub>H</sub> =5 V, internal pull-down) |                 |              |      |                 |      |                   |

| L-Input current (RST)                     | -IL             | -            | -    | 100             | μA   | -                 |

| (V <sub>H</sub> =0 V, internal pull-up)   |                 |              |      |                 | -    |                   |

| DATA OUTPUT                               |                 |              |      |                 |      |                   |

| L-Output current                          | ΙL              | -            | -    | 0.5             | μA   | -                 |

| $(V_{H}=0.5 V, open drain)$               |                 |              |      |                 |      |                   |

| H-Output current                          | I <sub>H</sub>  | -            | -    | 10              | μA   | -                 |

| (V <sub>H</sub> =5 V, open drain)         |                 |              |      |                 |      |                   |

## PULSE DURATION

| RST (address reset)  | t <sub>R</sub>  | 50 | - | - | μS | - |

|----------------------|-----------------|----|---|---|----|---|

| RST (set R – flag)   | ts              | 10 | - | - | μS | - |

| CLC (count, H-level) | t <sub>H</sub>  | 10 | - | - | μS | - |

| CLC (count, L-level) | tL              | 10 | - | - | μS | - |

| CLC (write, H-level) | t <sub>HW</sub> | 5  | - | - | ms | - |

| CLC (erase, H-level) | t <sub>HE</sub> | 5  | - | - | ms | _ |

## AC CHARACTERISTICS

| Delay time | t <sub>d1</sub>                     | 5   | - | - | μS | - |

|------------|-------------------------------------|-----|---|---|----|---|

| Delay time | t <sub>d2</sub>                     | 3.5 | - | - | μS | - |

| Delay time | t <sub>d9</sub>                     | 5   | - | - | μS | - |

| Delay time | t <sub>d10</sub>                    | 5   | - | - | μS | - |

| Delay time | t <sub>d3</sub> , t <sub>d4</sub> , | 3.5 | - | - | μS | - |

|            | t <sub>d5</sub>                     |     |   |   |    |   |

| Delay time | $t_{d6}, t_{d7}$                    | 5   | - | I | μS | - |

| Delay time | t <sub>d8</sub>                     | 10  | - | I | μS | - |

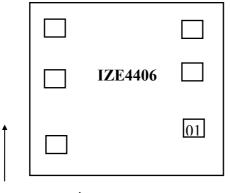

### CHIP PAD DIAGRAM

### Chip Size (mm): $x = 1,1\pm0.03$ , $y = 1,1\pm0.03$ Thickness of chip (mm): $0,18\pm0,01$

### PAD DESCRIPTION

| Pad<br>No. | Symbol | Description                                                                         |

|------------|--------|-------------------------------------------------------------------------------------|

| 01         | I/O    | Bidirectional data line<br>(open drain) Code entry on<br>"Input" only for transport |

| 02         | Р      | Test input                                                                          |

| 03         | CLC    | Clock input                                                                         |

| 04         | RST    | Control input (reset)                                                               |

| 05         | Vcc    | Supply voltage                                                                      |

| 06         | GND    | Ground                                                                              |

### PAD LOCATION

| Pad | Locatio   |          | Pad size,     |  |  |  |  |  |  |

|-----|-----------|----------|---------------|--|--|--|--|--|--|

| No. | Lower cor | ner), mm | mm            |  |  |  |  |  |  |

|     | Х         | Y        |               |  |  |  |  |  |  |

| 01  | 0.8530    | 0.2530   | 0,100 x 0,100 |  |  |  |  |  |  |

|     |           |          |               |  |  |  |  |  |  |

|     |           |          |               |  |  |  |  |  |  |

| 02  | 0.8530    | 0.6105   | 0,100 x 0,100 |  |  |  |  |  |  |

| 03  | 0.8530    | 0.8395   | 0,100 x 0,100 |  |  |  |  |  |  |

| 04  | 0.1530    | 0.8435   | 0,100 x 0,100 |  |  |  |  |  |  |

| 05  | 0.1530    | 0.5635   | 0,100 x 0,100 |  |  |  |  |  |  |

| 06  | 0,1440    | 0,1640   | 0,100 x 0,100 |  |  |  |  |  |  |